一些經典的運算放大器電路中運用了負反饋,因此通常就可以使運算放大器工作在線性區域內。

?

但是,也可以將運算放大器用作比較器,從而使其以非線性方式工作。由于其輸入受到硬驅動,因此其輸出電壓會對電源軌產生猛烈的沖擊。如下文所示,這可能并不總是一種好的設計方法。

?

變為非線性

在線性應用中,可以對運算放大器做如下理想假設:無限增益和帶寬、零輸出阻抗、無限輸入阻抗,以及輸入之間為零伏。也可以將運算放大器以非線性方式使用,但有一些地方要特別注意和處理。

?

一種常見的配置是僅使用開環運算放大器(無反饋),從而讓其高增益產生比較器工作。沒有負反饋,兩個輸入就不一定保持相同的電壓,因此上述第四點理想運算放大器假設也就無效。

?

圖1顯示了開環配置的運算放大器。當VIN大于零時,輸出電壓變高,并被限制在正電源電壓附近。當輸入電壓變為負值時,運算放大器輸出將擺動為負值,并再次被限制在負電源電壓附近。這里假設運算放大器是由常規的正負電源電壓供電。

?

圖1:將運算放大器用作零閾值電壓比較器。

?

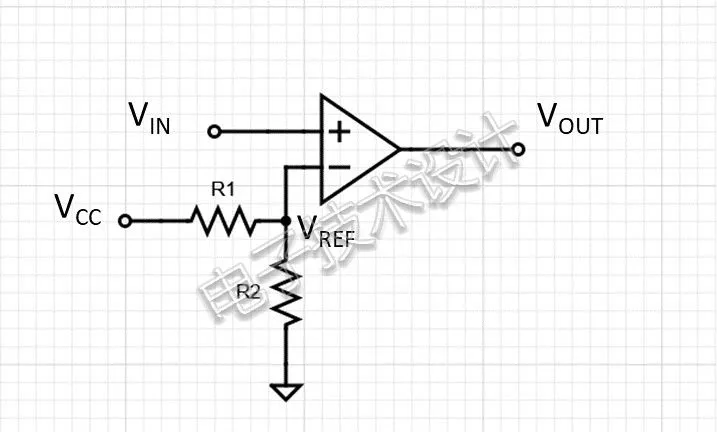

上述比較器電路在零伏附近工作。圖2在該電路中增加了一個電阻分壓器,對反相輸入端的電壓進行設置,從而提供了一種控制比較器參考電壓VREF的方法。

?

圖2:帶有電阻分壓器的運放比較器,可對閾值電壓進行設置。

?

圖3顯示了另一種常見的設計技術,即向比較器添加遲滯。在這種情況下,輸入電壓對運算放大器的反相輸入進行驅動,VREF則連接至同相輸入。R1-R2電阻分壓器從輸出VOUT產生VREF。當VIN降至VREF以下時,輸出電壓變高,從而導致VREF變成更高的電壓。

?

圖3:運放比較器電路通過正反饋來增加遲滯。

?

類似地,當VIN轉換為高于VREF時,VOUT變為最大負輸出電壓,從而將VREF拉低。這種遲滯效應在輸入信號上存在有任何噪聲時,就可以防止其在過VREF轉換時造成比較器工作反向。

?

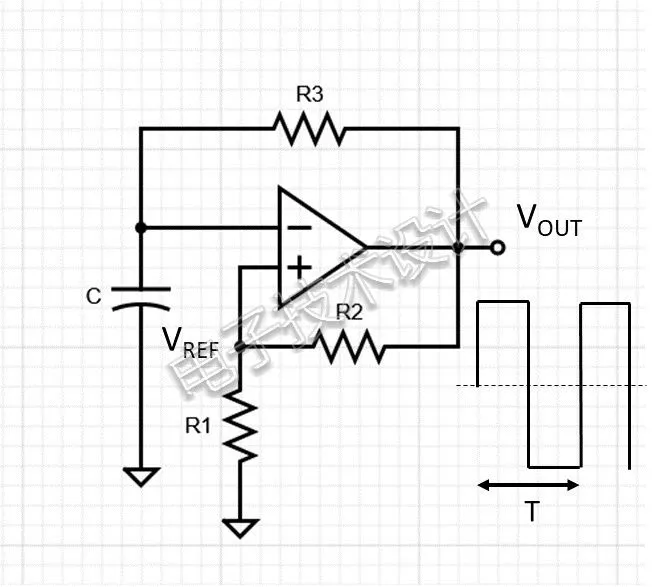

圖4中的多諧振蕩器電路使用圖3中的R1-R2遲滯電路以及RC定時電路來產生方波輸出。實際上,它不是比較器電路。取而代之的是,它將運算放大器用作比較器來創建所需的輸出波形。假設VOUT一開始為高電壓,那么它就會通過R3為C充電。電容器電壓就會增加,同時這個過程與時間常數R3-C保持一致。

?

圖4:多諧振蕩器電路添加RC定時電路以產生方波輸出。

?

當電容器電壓變得大于VREF時,輸出電壓將擺動至負電源電壓。這將導致電容器電壓被驅動為負,這個過程同樣與時間常數R3-C保持一致。R1-R2分壓器將在同相輸入上提供一定的遲滯,從而使運放實現平穩過渡。欲知有關元件值如何確定多諧振蕩器頻率的詳細信息,請參見參考文獻4。

?

但是有一些問題

網上有很多關于這類非線性運放電路的文章。但是,當我查看一些IC供應商的網站時,我注意到他們強烈警告不要將運算放大器用作比較器[參考文獻1和參考文獻2]。其主要問題包括:

?

一些運算放大器的輸入上有鉗位二極管,因此會限制兩個輸入之間的最大電壓。這可以通過精心設計或選擇其他運算放大器來解決。

?

比較器應用會將運算放大器驅動到飽和狀態。從飽和狀態恢復過來可能很慢,而且通常沒有指定。

?

大多數運算放大器的輸出電壓擺幅可能接近正負電源電壓。這可能有所指定也可能沒有,而且可能無法實現很好的控制。

?

與為該特定應用設計的“真實比較器”相比,運算放大器的開關時間趨于較慢。

?

運算放大器的輸出通常不設置為對數字邏輯進行驅動,因此可能需要使用其他電路來對其進行調整。

?

想要將運放用作比較器的主要原因可能是,有時使用一個多運放器件,正好剩余了其中一個放大器。畢竟,它就在那里,可以免費使用。如果您決定采用這種方法,則需要對數據手冊進行仔細研究,并評估實際電路性能是否井然有序。然后就是要確保運放電路具有相當大的內置裕量。

?

上述非線性運放工作的考慮因素,也可能有助于我們理解線性應用中可能出現的一些問題。是否有可能運放的輸出被驅動到軌電壓?如果是這樣,恢復需要多長時間?這對電路的性能有影響嗎?

?

因此,許多IC供應商都建議用戶使用真實的比較器而不是運算放大器。畢竟,比較器就是設計用作比較器。它具有指定的開關特性和輸出驅動,通常設置為用來驅動邏輯器件。有許多經濟型器件可供選擇。

2022-04-11

2022-04-11